问题分诊室

基于SiON/Al2O3叠层介质的薄势垒型HEMT栅极相关可靠性研究

发布时间: 2021-11-03

摘 要

本文工作中制备了基于SiON/Al2O3叠层栅介质的薄势垒型HEMT器件,在叠层介质的帮助下,器件的阈值电压与肖特基栅极器件几乎一致,可以实现常关型操作。其最大关态击穿电压可以达到700 V,栅极耐压超过23V,在超过1000s的正栅应力测试中阈值电压漂移量小于1V。通过对其关态击穿、栅极击穿、栅极应力测试等特性的分析,对其可靠性方面有更为深入的认识,同时进一步地展现出薄势垒HEMT器件的结构优势。

器件制备

本实验中准备的外延片是基于6英寸的Si片上通过金属有机化合物化学气相沉积(MOCVD)技术生长的AlGaN/GaN异质结,外延结构自上而下分别是30nm的Si3N4钝化层,4nm的Al0.23Ga0.27N势垒层,1nm的AlN插入层和4μm的GaN沟道层。具体工艺步骤如下:

(1)首先将样品依次浸没在有机、无机溶液中进行超声清洗,去除样品表面的沾污;

(2)利用电感耦合等离子体(ICP)刻蚀出器件所需的有源区图案,并切断器件与器件之间的漏电通路;

(3)在样品表面的固定区域沉积Ti、Al等金属,高温退火形成器件的源、漏欧姆接触电极;

(4)再次使用ICP设备刻蚀掉栅极区域附近的Si3N4钝化层,以形成栅槽。刻蚀至AlGaN势垒层时,刻蚀反应自动停止;

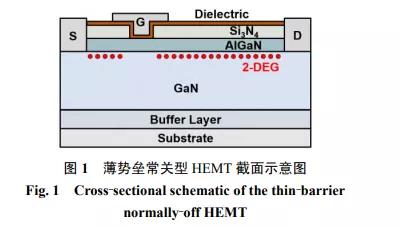

(5)在样品表面依次沉积10 nm-Al2O3(ALD)、20 nm-SiON(PECVD)薄膜,并进行400 ℃的快速热退火,记为样品A。样品B无介质沉积,作为空白对照组;(6)沉积金属Ni,以形成器件的栅极,完成器件制作。器件截面示意图如图1所示,其中栅、源之间距离LGS=2 μm,栅、漏之间距离LGD=16 μm,栅长LG=1 μm,栅宽WG=140 μm。

性能测试

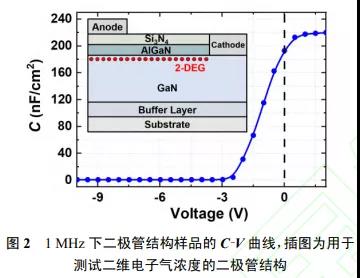

如图2所示,通过对曲线中的电容值对电压(从负值到0)做积分,便可估算出该样品的n2-DEG浓度为1.5×1012cm-2,由此可见2-DEG已经降到一个相对较低的值。

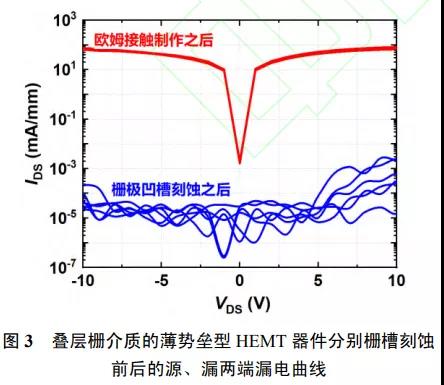

测量栅槽刻蚀前、后的源、漏极之间的漏电数据,其结果如图3所示。在VGS=10V时,样品的IDS从平均100 mA/mm直接降低5个数量级,基本可以实现阈值电压大于0(Vth>0V)的常关型操作。同时,该结果验证了Si3N4钝化的器件导通情况良好,而栅极区域的Si3N4被刻蚀后器件沟道关断,达到预期目标。

直流特性

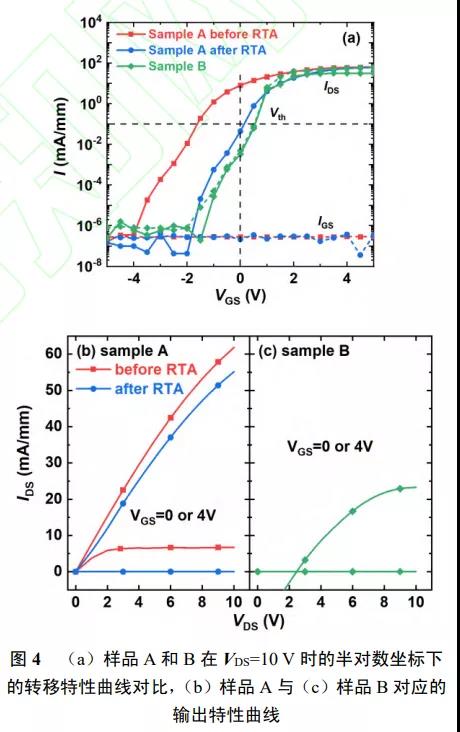

两样品的直流特性对比如图4所示,从转移特性可以看出在样品A退火后,Vth会发生明显的正向移动,这是因为Al2O3中的固定负电荷在退火之后浓度增大。选取IDS=0.1 mA/mm作为Vth参考点,三者Vth从小到大排列分别为-1.6、0.1、0.5 V,在Al2O3介质中的电荷调制作用下,退火后的样品A的Vth与样品B几乎一致,均可以实现常关型操作。在经过退火处理的器件A中,当VGS=0V时,器件的电流为0.04mA/mm,与器件完全开启时(VGS=5.0V)所对应的导通电流相差3个数量级,因此器件在VGS=0V附近被误开启的几率很低。此外,两个器件的电流开关比均大于108。

图4(b)和(c)展示了二者的输出特性对比,退火之后的样品A比退火之前的输出电流有降低,但可以保证VGS=0V时的输出电流可以被忽略。样品B由于肖特基栅极的原因,其导通电流最小,因为有一部分电流自栅极流出转化成IGS,这会造成IDS的分流。这里,较高的RSH和RC值共同造成了样品A的导通电流在VGS=4V状态下的IDS小于100mA/mm。

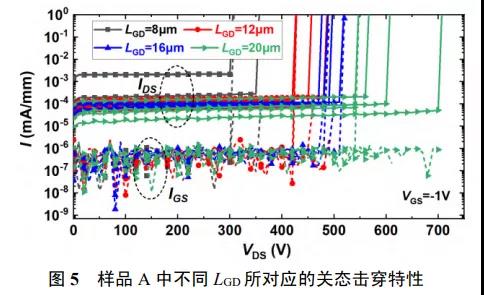

退火后的样品A在VGS=-1V时不同器件所对应的器件关态击穿特性曲线如图5所示,其中可以明显地观察到击穿电压(BV)随着LGD值的增加而增大,其中LGD=8、12、16、20μm所对应的BV平均值分别为324、453、498及610V。从图中还可以看出,并不是所有器件在击穿点附近都可以观察到IGS的上升,这证明引起器件击穿的原因并不全部在于栅极介质的损坏。

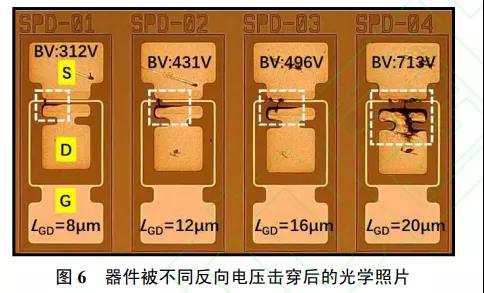

不同LGD的器件在关态击穿特性测试后的光学照片如图6所示。从图中可以看到,器件击穿是由于电极金属在高电应力条件下发生电迁移现象导致的。每个器件在击穿后源极和栅极、源极均有不同程度的金属“短接”,这是引起部分器件击穿后的栅漏电流上升的主要原因,该现象也从侧面说明了基于叠层介质的薄势垒器件栅极区域耐压程度较好。此外,LGD越大的器件,其所对应的BV越大,击穿后金属颜色发生转变的区域也就越大,证明其电极金属受电迁移应力越大。后续可采用在器件表面进行再钝化并设计场板结构来减弱电迁移效应,从而进一步提高器件的击穿电压。将器件的源、漏电极短接在一起,测试栅极耐压特性IGS-VGS特性如图7所示。在VGS<15V的范围内,栅极漏电低于10-6mA/mm,叠层介质的硬击穿点在23V左右,可以计算出其平均临界击穿电场超过7.5MV/cm,证明叠层介质本身的耐压能力良好。

栅应力结果

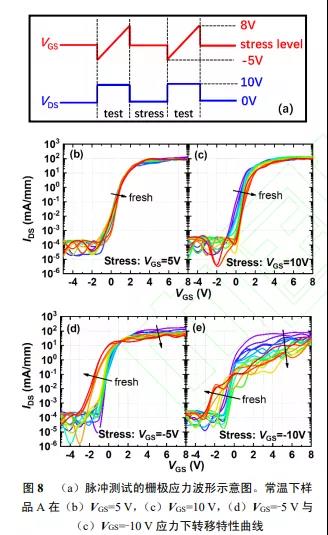

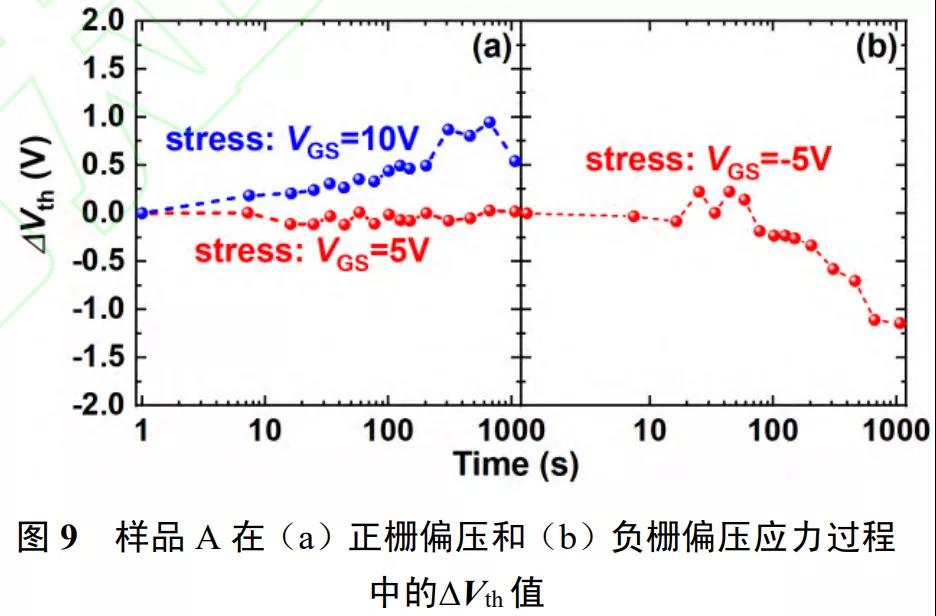

图8(a)为对器件A施加的栅极应力测试波形图,其中应力阶段VDS=0V,针对栅极施加了VGS=±5V与±10V的4个不同等级的应力。测试阶段统一采用VDS=10V,VGS进行从-5V到8V的扫描,应力测试时间共1000s,其结果如图8(b~e)所示。总地来说,器件在正栅压应力测试中的Vth漂移幅度小于负栅压应力测试,在正栅压应力测试中,可观察到Vth漂移方向为正,而负栅压应力测试中的Vth漂移方向相反。特别地,在VGS应力为-10 V的测试中,转移曲线退化较为严重,随着时间的增加,器件沟道在逐渐小的VGS处开启,但亚阈值摆幅(SS)明显增加。此外,还观察到器件的导通电流(VGS=8 V,VDS=10V对应的电流值)在该应力测试中有不同程度的衰退。测量施加应力后的Vth与器件起始Vth0之间的差值记为∆Vth,其具体值展示在图9中。VGS应力为5 V的测试中,∆Vth的绝对值小于0.2V,基本可以忽略;VGS应力为10V的测试中,∆Vth的小于1.0V;VGS应力为-5V的测试中,∆Vth对应的最大漂移点为-1.1V;而对于VGS应力为-10V的测试,因其转移特性退化太过明显,所以没有展示在图中。

上述结果是由应力测试中电子注入介质层的相关位置决定的。

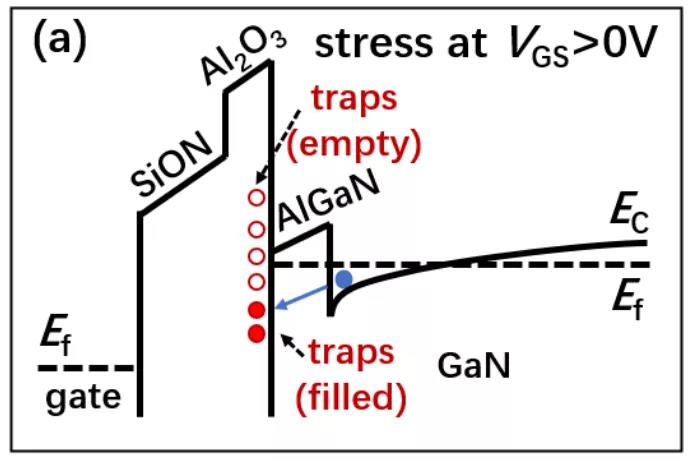

在正栅压应力测试中,其栅极区域附近的能带如图10(a)所示,电子在沟道中聚集,并且在电场的帮助下运动至Al2O3/AlGaN表面,被界面电荷所俘获,后续还可能注入到栅介质体中。当测试转移特性时,被占据的界面电荷将拉高势阱能带,导致Vth升高。而在负栅压应力测试中,其栅极区域附近的能带如图10(b)所示。在介质层中的陷阱辅助之下,电子由栅极注入进介质层中。此时测量转移特性时,介质层体内被陷阱俘获的电子将被释放到沟道中去,因此器件的沟道在一个更小的VGS处开启,导致Vth负漂。而在长时间测试当中,无论栅应力为正还是负值,被介质体内陷阱俘获的电子均会在器件开启后排斥沟道电子,进而致使导通电流值降低。结合图9可知,在栅压应力分别为正、负的两类测试中,电子从栅极注入介质层的难度比电子从沟道注入要低,因此器件在负的栅应力下退化更为明显。进一步地,可以将该现象概括为在器件开关过程中,电子从SiON一侧注入要比其从Al2O3一侧注入更加容易,对器件的阈值电压影响也更大。

结 论

本文工作对基于SiON/Al2O3叠层栅介质的薄势垒常关型HEMT器件进行了制备与研究。使用Si3N4/Al0.23Ga0.77N/AlN/GaN(30/4/1/4000 nm)的外延结构可以获得浓度为1.5×1012cm-2、迁移率达到1239 cm2/V·s的二维电子气。在基于该结构制备的器件阈值电压达到0.1V,并且可以实现常关型操作。此外,其最大关态击穿电压可以达到700V,击穿发生的原因为各电极在电应力作用下发生互联。而叠层介质的平均临界击穿电场超过7.5MV/cm,基于叠层介质结构的耐压性得到了验证。在对器件的栅应力测试中发现该器件在VGS=+10 V的测试中Vth漂移量小于1V,而负栅压应力测试中器件的转移特性退化更加明显。因此,电子从SiON一侧注入要比其从Al2O3一侧注入更加容易。

引自DT 新材料公众号