问题分诊室

IEDM:探究未来逻辑缩放 半导体行业观察

发布时间: 2021-01-11

在周一的IEDM上,Imec的Sri Samavedam在全体会议上以题为“未来逻辑缩放:通向原子通道和解构芯片”的演讲开启了该技术计划。我一般不喜欢全体会议的发言,我认为演讲者经常试图在会议中进行过多的报道,最终没有提供足够有用的细节,但是这次会议有很多很好的内容。

我要求Imec的幻灯片在本文中包括其中的一些,但是尽管确实向我发送了论文,但他们拒绝提供这些幻灯片。我感到奇怪的是,他们不提供幻灯片,幻灯片的视频演示位于IEDM网站上,可供注册的与会者查看,任何使用屏幕捕获实用程序的人都可以轻松捕获任何或所有幻灯片。我将利用论文中的几个数字来弥补幻灯片的不足。

演讲的大约前七分钟证明有必要继续开发领先的技术和某些历史观点,我将省略此部分,因为我相信Semiwiki阅读者和IEDM参与者已经了解了这一点。

EUV图案化

然后,讨论进入了EUV模式路线图。演讲者表示,他认为High-NA EUV将在2023年左右用于寻路,需要两到三年的时间才能投入生产。这将导致高净值EUV在2025/2026的时间范围内投入生产,比我预期的要晚得多。

Imec路线图针对的是3nm逻辑节点具有44-48nm的接触式多晶硅间距(CPP)和21-24nm最小金属间距(MMP),2nm逻辑节点是40-44nm CPP和18-21nm MMP以及1.5nm逻辑节点为40-44nm CPP和18-21nm MMP。我预计台积电将从2021年下半年的3nm节点开始,到2022年开始生产,而CPP和MMP将处于Imec提议的数字范围内。我预计台积电的2nm节点将在2023年开始冒险,并在2024年开始生产,并且CPP和MMP值将再次处于Imec提出的范围内。对于1.5nm,Imec并未显示出CPP和MMP范围的任何减小,这可能反映了堆叠晶体管的变化(稍后会详细介绍)作为一种驱动密度的技术。

Imec路线图显示了当前用于3nm和2nm的0.33NA EUV系统以及在1.5nm节点处引入的高NA(0.55NA),这再次比我预期的要晚。我曾有一段时间期望High-NA EUV会错过3nm节点(尽管其他人已经讨论了3nm的high-NA),但是我认为该系统将可用于2nm。如果High-NA EUV系统直到1.5nm才可用,那么严格来说,这将是一种降低成本的技术,因为1.5nm的间距与2nm的间距相同,并且2nm已经投入生产。几年前,我向ASML作了介绍,并提出了一个想法,即到高NA EUV可用时,晶体管堆叠(CFET)可能已变得无关紧要。与使用EUV进行多图案处理相比,High-NA EUV可能可以降低成本,

我联系ASML对此发表评论,并得到以下答复:

“我们正在与客户就批量生产中插入高NA的路线图时间进行协调,目前估计在2025年至2026年的时间范围内。我们将与他们合作,尽快升级到HVM。回顾以前的过渡,例如ArFi,通常在第一批工具交付后需要几年时间才能升级到HVM。因此2025年至2026年的HVM时序将帮助我们的客户减少对EUV多重图案的使用,并在成本,工艺复杂性和周期时间方面带来好处。”

逻辑缩放

演示中我最喜欢的幻灯片之一是Logic Scaling Roadmap幻灯片,幸运的是,它是本文中的一个图(请参见图1)。

图1.逻辑扩展路线图

对于3nm节点,Imec显示了一个基于FinFET的5轨高度单元,我相信这是台积电采用的方法。另一方面,三星宣布他们将在3nm处使用Gate All Around(水平纳米板,HNS),我相信这将是一个6轨高度的单元,因为要使用HNS达到5轨需要埋入电源导轨(BPR) ),而BPR尚未准备好生产(根据两家公司宣布的密度改进,三星3nm的密度将大大低于台积电3nm)。

在2nm处,可以选择使用BPR的5轨HNS,甚至是带有叉板(FS)的HNS,以实现少于5轨的单元(作者注:通过组合HNS,BPR和FS可能达到〜4.33轨) 。

前进到具有nFET和pFET堆叠以及4轨单元的1.5nm CFET可以提供缩小,同时保持与2nm相同的间距。Imec对CFET进行了大量研究,英特尔在会议上发表了一篇有关CFET的有趣论文,该论文利用堆叠中的三个pFET和两个nFET来匹配两种设备类型的性能,而Synopsys也在CFET上发表了一篇论文,我是其中的合著者。

对于1nm或更高的波长,Imec正在研究2D原子通道和少于4条轨道的单元。我知道还有一些工作可以通过堆叠更多的层来进一步扩展CFET。2D原子通道将像纳米片一样堆叠,但是由于极薄的层可能以相同的功率提供更高的频率性能。

该演示继续进一步讨论了BPR。BPR可以降低功率传输阻力,从而提高功率效率,并通过在基板中形成高金属线来代替互连层中的宽金属线来减小面积。BPR还可以在通过使用硅通孔(TSV)的方式连接到BPR的晶圆背面实现电源传输网络,尽管这需要非常小的“纳米” TSV。利用晶片的背面进行功率传输还将使金属绝缘体金属(MIM)电容器和静电放电(ESD)保护二极管集成到背面。

除了2D原子沟道晶体管以外,Imec还研究了包括量子计算量子位在内的各种选择。

BEOL路线图

从线路的后端(BEOL)看,Imec认为铜双镶嵌可以缩小到21nm的间距,但是通孔电阻将是一个问题。为了解决通孔电阻问题,需要一种混合方案,其中通孔是用诸如钌,钼或钨的替代材料制成的。Imec路线图中将3nm节点工艺定义为节距为21-24nm,因此标准双镶嵌铜对于3nm节点可能是可以的。在Imec路线图中,2nm节点的金属间距为18-21nm,因此最关键的层可能需要混合金属化。

超过21nm的间距,减法金属图案变得有吸引力,以使具有部分或全部气隙的高深宽比金属线能够解决线间电容问题。由于铜很难蚀刻,因此减法金属化将需要新的金属,例如钌或钼。半金属镶嵌(具有减法图案)和气隙的组合导致互连电阻(RC)的显着降低。Imec已经展示了32nm间距,目前正在研究18nm间距。最初的18nm结果显示出更好的RC性能,但仍需要在自对准通孔和气隙制造上进行工作。Semi大马士革是1.5nm节点的候选者。

除了1.5nm节点以外,Imec正在研究替代材料。尺寸非常小的材料的品质因数是体积电阻率乘以电子平均自由程,这是因为在尺寸较小的材料中,具有较长电子平均自由程的材料的电阻率会显着增加。Imec已在仿真中确定了几种有前途的合金,并需要克服集成挑战并证明材料在实际设备上是可行的。

SRAM缩放

通过设计技术共同优化实现了持续的逻辑缩放,从而实现了磁道高度的减小,但这并没有延续到SRAM单元中。SRAM单元的大小曾经按每个节点的50%缩放,但缩放速度变慢了。转向HNS将提供一些浇口长度缩放,但对纸页宽度的限制将限制缩放。FS可以提供缩放比例提升,而CFET可以提供额外的降低。

还有机会利用顺序的3D集成方案并在预处理晶片上的SRAM阵列上制造逻辑,但是这种技术将需要对逻辑进行低温处理而不会影响性能。

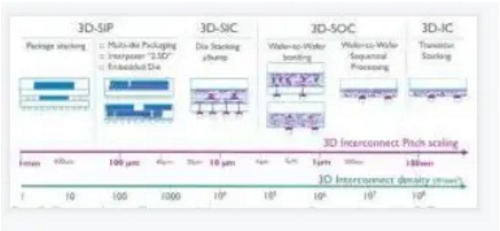

解构芯片

功能越来越强大的3D集成方案提供了将芯片解构为多个芯片的能力,每个芯片都针对其功能进行了优化。将复杂的片上系统(SOC)设计分解为小芯片将允许优化的小芯片,例如,一个小芯片可以是处理器核心,其他小芯片可以是SRAM缓存低级缓存,MRAM或DRAM,用于更高级别的缓存或主存储器。集成了非常高的带宽。用化合物半导体制造的专用设备也可以集成。为了充分发挥解构3D集成在晶片间键合方面的全部潜力,需要克服微凸点和功耗方面的挑战。

结论

这里讨论的技术提供了十到十五年的逻辑缩放。具有0.33NA到高NA(0.55NA)过渡的EUV图案,HNS,FS,BPR,PDN,CFET和2D原子通道,新的SRAM缩放技术和3D集成都是未来逻辑技术的有希望的候选者。